Research Article | Open Access

|

Open Access

|

| Published online: 23 September 2025

The Unified Neuromorphic Assembly Layer for Hardware-Agnostic

Compilation in Neuromorphic Computing

| Published online: 23 September 2025

The Unified Neuromorphic Assembly Layer for Hardware-Agnostic

Compilation in Neuromorphic Computing

Ganesh D. Jadhav,1,* Rahul V. Dagade,2 Sushant Jakhade,1 Kshitij Jadhav,1 Rutu Hinge1 and Swarada Joshi1

1 Department of Information Technology, Vishwakarma Institute of Technology, Pune, Maharashtra, 411037, India

2 Department of Computer Engineering, Vishwakarma Institute of Technology, Pune, Maharashtra, 411037, India

*Email: jadhavganesh874@gmail.com(G. Jadhav)

J. Smart Sens. Comput., 2025, 1(3), 25212 https://doi.org/10.64189/ssc.25212

Received: 14 November 2025; Revised: 20 December 2025; Accepted: 22 December 2025

Abstract

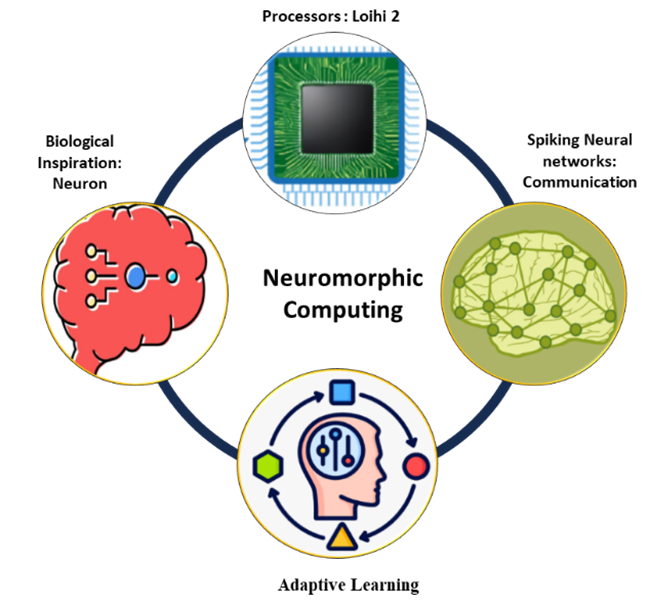

The programming of neuromorphic assembly has advanced steadily, providing essential tools and paradigms to help connect the gap between abstract Spiking Neural Network (SNN) models and brain inspired computing hardware. This work presents UNAL (Unified Adaptive, Hardware-Agnostic Neuromorphic Assembly Layer). This compilation framework translates high-level Spiking Neural Network (SNN) models into portable, spike-level assembly across heterogeneous neuromorphic platforms. UNAL introduces a unified intermediate representation (UNAL-IR), a compact instruction set, and an optimization driven mapping pipeline that jointly addresses latency, energy efficiency, routing congestion, and adaptability. Quantitative evaluation on standard SNN benchmarks (DVS Gesture and CIFAR-10 SNN) mapped to Intel Loihi 2 demonstrates 18–32% latency reduction, 21–38% energy savings, and 25–40% lower routing congestion compared to Loihi-native and platform-specific tool chains. A smart-city surveillance case study further validates the deployment of real-time edge computing. These results establish UNAL as a scalable and future-ready neuromorphic compiler infrastructure.

Graphical Abstract

Novelty statement

This work introduces a hardware-agnostic neuromorphic compilation approach that unifies heterogeneous SNN execution models, supports adaptive neural dynamics, and automates spike-level instruction synthesis.